65 lines

2.8 KiB

Markdown

65 lines

2.8 KiB

Markdown

> 工艺角(Process Corner)是集成电路(IC)设计中的核心概念,用于量化**芯片制造过程中的工艺波动对晶体管性能的影响**。

|

||

|

||

---

|

||

|

||

1.工艺角的本质

|

||

|

||

芯片制造存在不可避免的物理波动(如光刻偏差、掺杂不均匀),导致同一晶圆上不同区域的晶体管参数(阈值电压 )、载流子迁移率 )、栅氧厚度 ) 等)偏离设计值。

|

||

|

||

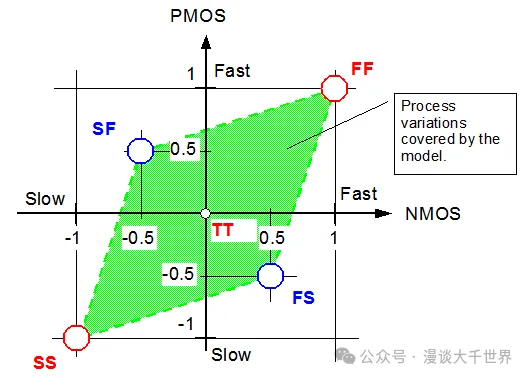

工艺角通过组合 **NMOS** 和 **PMOS** 晶体管的 **“快”(Fast)** 与 **“慢”(Slow)** 两种极端状态,模拟性能边界。

|

||

|

||

|

||

|

||

> **关键公式**:晶体管驱动电流

|

||

>

|

||

> **“快”晶体管**: 低 + 高 → 大 → 开关速度快

|

||

>

|

||

> **“慢”晶体管**: 高 + 低 → 小 → 开关速度慢

|

||

|

||

---

|

||

|

||

2.工艺角分类

|

||

|

||

|**缩写**|**NMOS状态**|**PMOS状态**|**芯片特性**|**核心应用场景**|

|

||

|---|---|---|---|---|

|

||

|**TT**|典型 (Typ)|典型 (Typ)|设计中心值|功能验证、基准性能评估|

|

||

|**FF**|快 (Fast)|快 (Fast)|**速度最快,功耗最大**|最大频率(Fmax)、最坏功耗分析|

|

||

|**SS**|慢 (Slow)|慢 (Slow)|**速度最慢,功耗最小**|建立时间(Setup)验证、漏电流分析|

|

||

|**FS**|快 (Fast)|慢 (Slow)|NMOS快 + PMOS慢|对PMOS敏感路径的保持时间(Hold)检查|

|

||

|**SF**|慢 (Slow)|快 (Fast)|NMOS慢 + PMOS快|对NMOS敏感路径的建立时间(Setup)检查|

|

||

|

||

---

|

||

|

||

3.工艺角如何影响芯片性能?

|

||

|

||

##### 3.1. **时序性能**

|

||

|

||

- **FF角**:路径延迟最小 → **易发生保持时间违例**(信号过早到达)

|

||

|

||

- **SS角**:路径延迟最大 → **易发生建立时间违例**(信号过晚到达)

|

||

|

||

- **FS/SF角**:特定路径延迟异常(如FS角下PMOS延迟主导的路径变慢)

|

||

|

||

|

||

##### 3.2. **功耗特性**

|

||

|

||

- **静态功耗**:在 **SS + 高温** 下最大(高温指数级增加漏电流)

|

||

|

||

- **动态功耗**:在 **FF + 高压** 下最大(高压 & 高翻转率)

|

||

|

||

|

||

##### 3.3. **可靠性风险**

|

||

|

||

- **FF + 高压 + 高温**:电迁移(EM)、自发热问题加剧

|

||

|

||

- **SS + 低压 + 高温**:晶体管驱动能力不足导致功能失效

|

||

|

||

|

||

---

|

||

|

||

4.为什么工艺角不可或缺?

|

||

|

||

4.1. **鲁棒性保障**:预判硅片制造中的波动极限,避免芯片失效。

|

||

4.2. **PPA平衡**:在性能(Performance)、功耗(Power)、面积(Area)间找到最优解。

|

||

4.3. **良率锚点**:Corner覆盖越充分,量产良率越高。

|

||

4.4. **设计迭代依据**:通过Corner仿真定位薄弱电路,指导优化方向(如调整晶体管尺寸、缓冲器插入)。 |