30 lines

2.9 KiB

Markdown

30 lines

2.9 KiB

Markdown

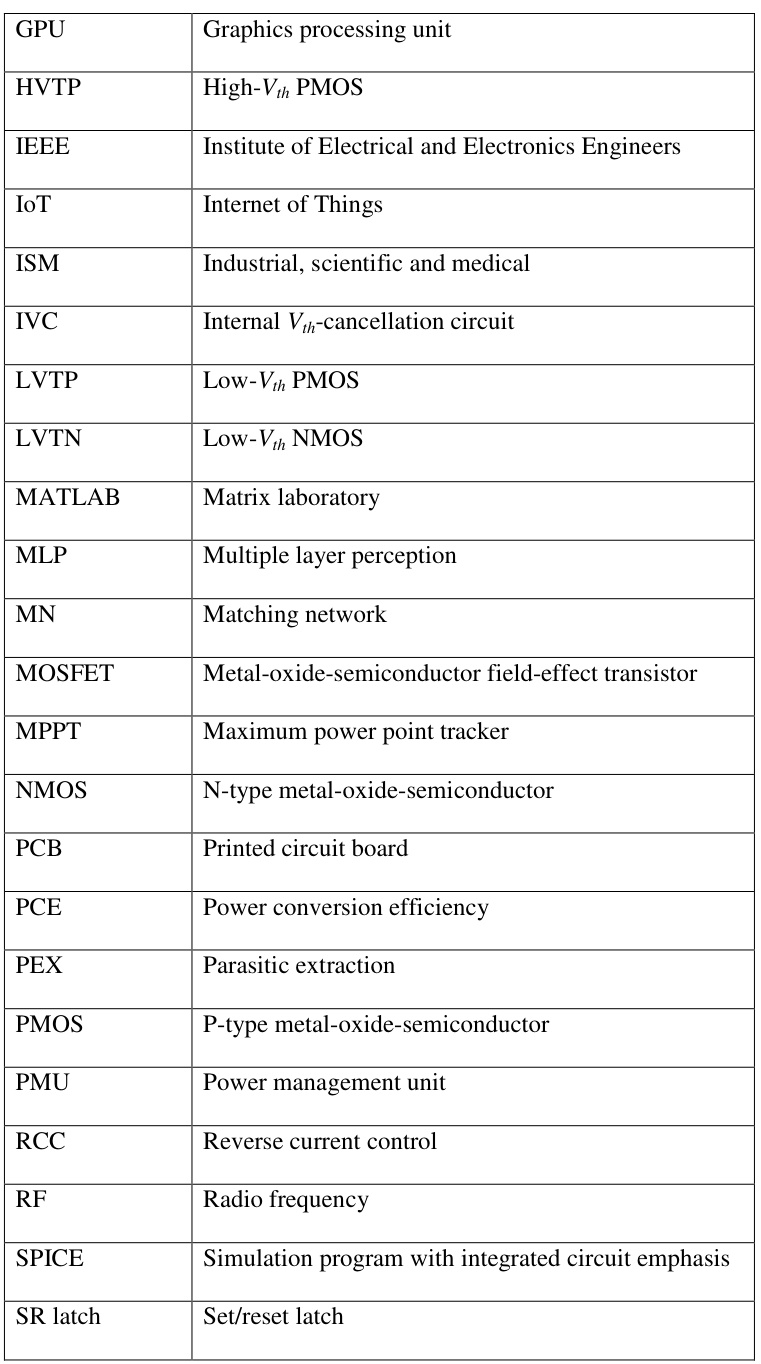

- 参数表 ![[acfa54e3bc145c6d50a14df5d4c22812.png]]

|

||

- Corner NN/TT

|

||

- **LVTN(Low Threshold Voltage NMOS)**

|

||

- **定义**:指**低阈值电压的N型金属氧化物半导体场效应晶体管**(NMOS)。通过降低器件开启电压(VthV_{th}),可提升电路在低电压下的开关速度,但会增加静态功耗。

|

||

- **工艺特性**:通常需通过**离子注入调整沟道掺杂浓度**实现低阈值(如中的LVTN与LVTP对应低阈值PMOS/NMOS晶体管)。在先进制程(如28nm以下)中,LVTN常与HVT(高阈值)器件组合使用,以平衡速度与功耗。

|

||

- **LVTP(Low Threshold Voltage PMOS)**

|

||

- **定义**:**低阈值电压的P型金属氧化物半导体场效应晶体管**(PMOS),与LVTN构成互补结构。用于低电压驱动电路或高速逻辑单元设计。

|

||

- **应用场景**:在电源管理芯片(PMIC)中,LVTP可优化转换效率(如提到的HVTP/LVTP与LVTN的组合设计)。

|

||

- **RVTN(Regular Threshold Voltage NMOS)**

|

||

- **定义**:**常规阈值电压的NMOS**,是标准逻辑单元的基础器件。阈值电压介于LVT(低阈值)与HVT(高阈值)之间,兼顾速度与功耗。

|

||

- **工艺兼容性**:在90nm以下工艺中,RVT、SVT(标准阈值)、LVT等可通过调整**掺杂浓度**和**栅极功函数金属层**实现,且RVT通常无需额外掩模层(如所述)。

|

||

- **RVTP(Regular Threshold Voltage PMOS)**

|

||

- **定义**:**常规阈值电压的PMOS**,与RVTN配合构成标准CMOS单元。在数字电路设计中广泛用于平衡时序和漏电流。

|

||

- **SLVTN/SLVTP(Super Low Threshold Voltage NMOS/PMOS)**

|

||

- **定义**:**超低阈值电压的NMOS/PMOS**,阈值电压比LVT更低,适用于超低功耗或亚阈值电路设计。

|

||

- **技术挑战**:需严格控制工艺波动,避免因阈值电压过低导致漏电剧增。在物联网(IoT)传感器芯片中常用于延长电池寿命。

|

||

- **总结与术语对照表*

|

||

-

|

||

|

||

| 缩写 | 主要领域 | 全称/定义 |

|

||

| ----- | ------------ | ------------------------------------- |

|

||

| LVTN | 半导体制造 | 低阈值电压NMOS晶体管 |

|

||

| LVTP | 半导体制造/医学/计算机 | 低阈值电压PMOS晶体管 |

|

||

| RVTN | 半导体制造 | 常规阈值电压NMOS晶体管 |

|

||

| RVTP | 半导体制造/金融/交通 | 常规阈值电压PMOS晶体管 / 已实现方差期限溢价 / 罗阿诺克谷交通规划 |

|

||

| SLVTN | 半导体制造 | 超低阈值电压NMOS晶体管(推测性定义,资料未明确提及) |

|

||

| SLVTP | 半导体制造 | 超低阈值电压PMOS晶体管(推测性定义,资料未明确提及) |

|

||

|

||

- UUID

|

||

- Lot ID/ Wafer ID/ Wafer X/ Wafter Y |